投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

数控系统中的光纤串行通信

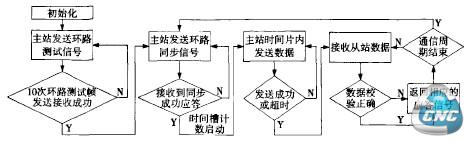

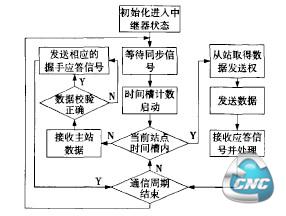

(5)主站和各个从站收到同步信号时,一个数据传输周期开始,主站和各个从站的时间计数器模块开始计数,在通信周期内,各个站根据自己的地址和当前计数值,确定哪个时间槽属于该站点,当属于自己的时间槽到来时,该站点便拥有总线的数据发送权,向总线发送数据;数据传输周期开始后,主站在属于自己的时间槽内往从站发送数据。与此同时,主站接收ISA总线数据并对数据进行标志、缓存,完成数据的编码,实现握手机制,超时重发、出错重发,对发送数据进行并串转换及对接收的数据进行串并转换。

(6)主站发送一帧数据后,等待相应从站的应答信号,若收到从站的负应答信号,表示数据没有被从站正确接收,主站将重发上一帧数据并再次等待从站的应答信号,若连续两次收到从站的负应答信号,则产生错误中断并返回步骤(2);若收到从站的正应答信号,表示数据被从站正确接收,主站在自己的时间槽内继续发送下一帧数据,若没有新的数据发送则等待该时间槽的结束。

(7)主站时间槽结束后,从站在属于自己的时间槽内往主站发送数据,从站发送一帧数据后,等待主站的应答信号,若收到主站的负应答信号,表示数据没有被主站正确接收,从站将重发上一帧数据并再次等待主站的应答信号,若连续两次收到主站的负应答信号,从站产生错误中断并返回等待新一次的同步信号;若收到主站的正应答信号,表示数据被主站正确接收,从站在自己的时间槽内继续发送下一帧数据,若没有新的数据可以发送则等待该时间槽的结束。

(8)主站和各个从站的时间计数器模块计数到设定值时,当前数据传送周期结束,主站返回步骤(2),等待处理器指令或开始下一次数据传送周期,从站等待主站的同步信号。

以上阶段依次进行,不断循环,直到控制器终止传输或者环路传输错误被迫中断。

主站协议及从站协议的控制主体流程图如图4、图5所示。

3.3 数据编码特点

在曼彻斯特编码和差分曼彻斯特编码中,每位中间都有一次电平跳变,因此波特率是数据速率的2倍。对于lOOMbps的高速网络,若采用该类编码方式,就需要200M的波特率,硬件成本是lOOM波特率硬件成本的5-10倍。

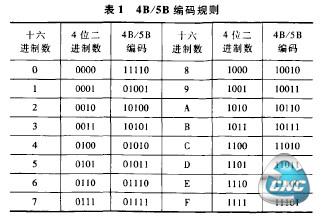

本系统的通信协议直接对基带进行编码,以适合光纤作为通信介质的传输方式。为提高编码效率,尽量减小硬件开销,同时方便同步信号的提取,这里采用4B/5B码对源码进行编码。例如,用于同步的报文起始符为连续的15个0,通过4B/5B编码可以有效地消除源码中可能存在的这种码组。4B/5B编码的规则如表1所示。

5位二进制代码的状态共有25=32种,从中取1的个数不少于2个的状态来表示0~F,这样就可以保证在介质上传输的代码能提供足够多的同步信息。

4 联合通信仿真及结果分析

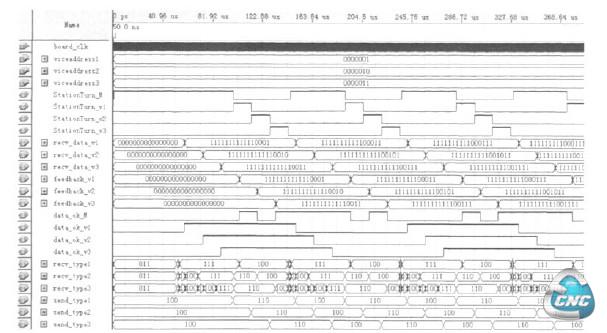

在QuartusU6.0软件环境下设计好主从站各模块VHDL代码。为模拟主从站通信,设计一个新的顶层文件调用主从站模块,用该模块调用1个主站、3个从站。通过该顶层文件,仿真主站与3从站之间的数据通信。主站从站联合仿真通信的结果如图6所示。

仿真时,由主站给各从站发送数据,各从站接收到相应的数据后,立即将接收到的数据重新发送给主站。根据各从站接收到的数据和主站接收到的数据,可以判断环路通信是否正常。

图6中,系统时钟board—clk设为100MHZ。viceaddressl、viceaddress2、viceaddress3分别为3个从站的ID号。StationTurn—M、StationTurn—vl、Station-Turn—v2、StationTurn—v3分别标志了主站及3个从站的数据发送权,高电平表示当前时间属于该站,该站具有数据发送权。reev—data—vl、reev—data—v2、recv—data—v3分别表示各从站接收到的数据,feedback—vl、feedback—v2、feedback—v3则分别表示各从站发送给主站的数据,这主要是模拟伺服电机编码数据的反馈o data—ok—M、data—ok—vl、data—ok—v2、data—ok—v3分别标志主站及各从站数据接收是否正确,若接收正确则电平翻转。recv—type和send—type则分别指示各从站在数据接收、发送过程中的状态,当环路通信出错时,可根据这些状态的显示去定位问题所在。主站发往从站1、从站2、从站3的数据分别初始化为X”fffl”、x”fff2”、X”fff3”,随后发送的数据则循环左移一位,发送时间间隔略大于通信周期,为100us(设置的协议通信周期为90us)。由结果可知,该通信协议能准确无误地实现主从站点间的数据传输。根据设计,该通信协议能够达到的最高有效数据传输速率为5.33Mb/s。如果对系统时钟进行倍频处理,该速率还可以进一步提高,如:系统时钟频率提高至150MHZ,最高有效数据传输速率为8Mb/s。

5 结束语

本文通过设计串行通信协议,并借助FPGA构建主从站,仿真实现了数控系统中基于光纤的环路高速串行通信。该设计目前已经在实际数控系统中得到成功运用,其简便灵活、高实时高稳定的性能很好地解决了传统数控系统存在的不易扩展、通信可靠性不高等问题。该设计为数控系统的开放性研究提供了一个很好的发展方向,后期可进一步通过优化VHDI.代码,改善通信部分细节,缩短通信周期等方式提高其通信性能。

- 第1页:数控系统中的光纤串行通信(1)

- 第2页:数控系统中的光纤串行通信(2)

- 上一篇文章:数控切割FastCAM套料软件使用探讨

- 下一篇文章:数控车床电动刀架故障的深度剖析