投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

多轴联动高速运动控制网络的设计与实现

4 网络实现及仿真实验

4.1 节点控制芯片功能仿真实验

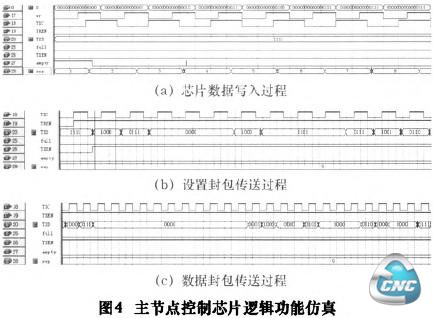

利用上述逻辑控制芯片的逻辑结构、数据格式、状态字以及数据传输过程,根据模块设计不同的VHDL进程Process,完成主/从控制芯片逻辑设计。主节点控制芯片逻辑功能仿真如图4所示。

图4a为数据写入过程,发送队列空标志empty迅速拉低。WR的升沿上,16位数据总线将数据0000H一0007H依次写入芯片FIFO,指针XWP递加。图4b的参数设置,发送允许TREN为高,TXD响应发送时钟TXC降沿,依次送出封包起始字“1000”与校验字“0111”,而后送出节点地址00H与数据封包长08H及其组合后的反码0FFF7H,最后送出结束字“1001”与校验码“0110”,结束参数设置段。

数据封包的发送如图4c,在TXC的降沿上,TXD依次送出起始字与校验码“1000”、“0111”,数据0000H及校验码0000H,数据0001H及16位循环冗余码8005H,数据0002H及冗余码800FH,输出顺序与图4a中写入的数据及顺序严格对应。

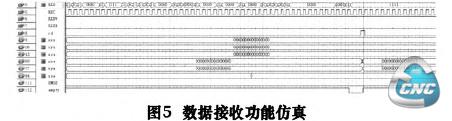

从节点控制芯片功能仿真如图5,图中所述为空间直线运动指令的传输。传输结束前接收队列空标志empty为1,实际上此时数据已经写入队列,为保证数据可靠性,此时不允许读取正在传送的数据封包。传输结束,队列空标志复位,读信号RD上升沿,接收队列中数据送出,图中运动模式XMOD=0,即直线运动,终点菇坐标蛳e=3(0011B),Y坐标xye=4(0100B),z坐标xze=0,起点坐标全为0。

4.2硬件实现

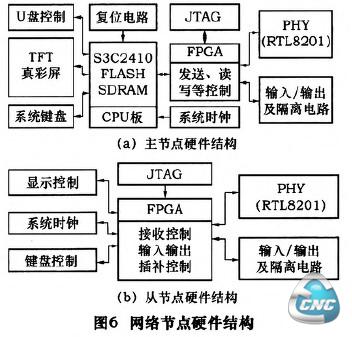

网络节点的硬件结构如图6所示。主节点硬件由CPU模块、主节点控制芯片(FPGA)、USB控制、系统键盘、物理层接口PHY及必要的IO电路构成。CPU采用集成的CPU板,板上集成嵌入式处理器S3C2410、64 MB的SDRAM、2 MB的Nor Flash与64MB的Nand Flash,显示模块为商用的3.5英寸TFr真彩屏,PHY器件采用常用网络接口器件RTL8201。

上述硬件结构中,主节点处理器$3C2410通过u盘控制获取U盘中的指令数据,译码后将结果写入主节点控制芯片(FPGA)的FIFO,经过网络发至从节点,由从节点输出相应的插补脉冲、方向信号以及其他开关控制信号。网络硬件设计中采用两组收发器,形成冗余网络,增强网络的可靠性。主节点TFT模块显示主节点以及从节点的状态信息、正在运行的程序段等内容,节点选择、文件操作等的通过主节点键盘完成。图7为网络实验的结果。根据图6描述的硬件结构,不考虑CPU模块,主/从节点具有相似的硬件结构,因而,本文的网络实验中从节点硬件与主节点的采用了同样的控制板,只是从节点上省去了CPU板和TFT模块。

5 总结

根据运动控制网络的发展,结合其在数控技术领域的应用,参考现有运动控制总线Synqnet网络,提出适于数控领域的一套类Synqnet网络结构及其实现技术,这种结构在节点上固化多轴联动控制逻辑,使每个运动控制网络节点成为一个独立的多轴运动控制器,节点上的多轴联动通过节点控制芯片实现,无需专门的CPU。同时,节点带有FIFO,能够满足联动控制的高实时性要求及网络化要求;结合数控技术,提出一整套的类Synqnet协议并提出其VHDL实现方法;在此基础上,采用硬件描述语言VHDL,完成了主节点逻辑控制芯片与具有多轴联动功能的从节点逻辑控制芯片设计。最后,利用商用的嵌入式S3C2410 CPU板,开发节点硬件对所提出的网络与通信协议进行了验证。

- 上一篇文章:网络化数控加工中数据传输方法研究

- 下一篇文章:基于PLC的变频控制系统在纸业浆泵上的设计