投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

基于数控流水线技术的开放式数控系统(下)

2.3.1 数据缓冲区

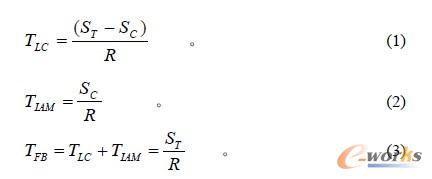

数据缓冲区包括 NCM 缓冲区和状态信息区。NCM 缓冲区暂存数控主控流水线线程产生的NCM流数据。状态信息区内保存NCMP 采集的当前状态信息。NCM 缓冲区的延时效应隔离了数控流水线的实时部分和非实时部分,其大小影响着系统的性能。假设NCM 缓冲区的总大小为ST 字节,而当NCM 缓冲区中未执行的NCM 代码小于临界值SC字节时通知数控主控流水线线程写入新的NCM 代码。设NCM 代码的执行速率为R 字节/秒,则可确定如下关系式:

其中,TLC 代表NCMP 从缓冲区满到缓冲区内未执行NCM 代码等于SC 的运行时间,TIAM 表示从NCMP 发出唤醒请求到流水线线程运行并开始将新一批NCM 代码写入缓冲区之间允许的最大延迟时间。TFB 代表整个缓冲区内NCM 代码对应的总运行时间。相关的时序关系如图6 所示。其中,TS代表流水线线程休眠时间,TR 代表流水线线程运行时间。TIA 表示从NCMP发出唤醒请求到流水线线程运行并开始将新一批 NCM 代码写入缓冲区的延迟时间。图6a 是正常情况下的时序,图b 是缓冲区大小设置不妥,操作系统不能及时调度进入错误状态的情况。综合以上可知,应设置足够大的ST 和SC 的数值,保证时间TFB 和TIAM 足够长。还要注意TLC 不要太小,否则会导致流水线线程休眠到运行的调度过于频繁,降低系统效率。同时,ST 也不能过大,否则缓冲区的延时效应会产生能使数控系统操作人员发觉的明显延迟。

图 6 NCMP 与数控主控流水线线程状态的时序关系

2.3.2 NCMP 主控制器

NCMP 主控制器是NCMP 的中央处理器,主要功能是根据微代码实时控制相应的NCM 执行器件执行NCM 代码。主控制器上NCM 代码的执行流程如图7 所示。此外,它还负责采集和刷新状态信息,以及与上位机进行直接的快速通信等。由于NCM 代码是功能十分精简的“原子”操作,非常容易实时执行,因此与传统的运动控制卡不同,NCMP 主控制器通常并不需要高性能的嵌入式处理器(如DSP 等),只需采用低端的嵌入式处理器即可满足要求。这样既降低了NCMP 的成本,又简化了NCMP 的设计,提高了可靠性。

2.3.3 NCM 执行器件

NCM 执行器件是NCM 代码直接执行单元,按照NCM 代码类型的不同划分为不同的执行器件,每一种执行器件对应执行一类NCM 代码。由于NCM 代码的执行逻辑固定而简单,且实时性非常强,因此宜采用硬件电路实现。当前PLD 器件具有设计灵活,可重构,集成度高,速度快,成本低等优点,因此可以将多个NCM 执行器件集成在一片PLD 中,既能很容易达到NCMP 的设计要求,又具有很强的灵活性。

2.3.4 机床信号变换与隔离部分

这部分功能主要是电气信号的变换。

2.3.5 NCMP 重构接口

NCMP 重构接口可以对NCMP 主控制器和NCM 执行器件的逻辑进行更改,进而对NCMP 进行软硬件的重构,因此NCMP 的控制逻辑对用户是开放的。重构是基于NCMP 硬件的在系统编程(In-System Programming, ISP)和在应用编程(In-Application Programming, IAP)技术。通过开放ISP 或IAP 接口,用户可以对NCMP 进行开发,实现重构。

2.4 软件开发标准

数控流水线的软件开发包括数控主控流水线线程的软件开发、NCMP 主控制器的软件开发和NCMP 执行器件逻辑功能的开发。数控主控流水线线程应遵循NCCC 和NCM 接口标准,采用模块化方法设计,实现不同版本的模块的互换。模块按照开放程度的不同,可以提供源代码、静态链接库或动态链接库文件进行编译或链接。其中,源代码开放方式具有最大的跨平台开放程度。NCMP主控制器的控制软件采用标准ANSI C 编写。ANSI C 被多数微控制器的调试环境支持,可保证控制软件不依赖于具体厂商的微控制器,具有良好的移植性和开放性。因主控制器的任务极其简单,控制软件可采用标准框架式的设计,开发者在程序框架内很容易扩展NCM 代码和状态采集等功能。NCM 执行器件的控制逻辑主要由PLD 内的逻辑决定。这部分逻辑功能的开发采用VHDL 和VerilogHDL 这两种国际标准[15] 的硬件描述语言(Hardware Description Language, HDL)开发,每一个NCM器件均可作为HDL 源程序的一个模块。

3 实验

3.1 实验平台

为验证数控流水线技术的效果,设计了一个数控系统的实验平台。

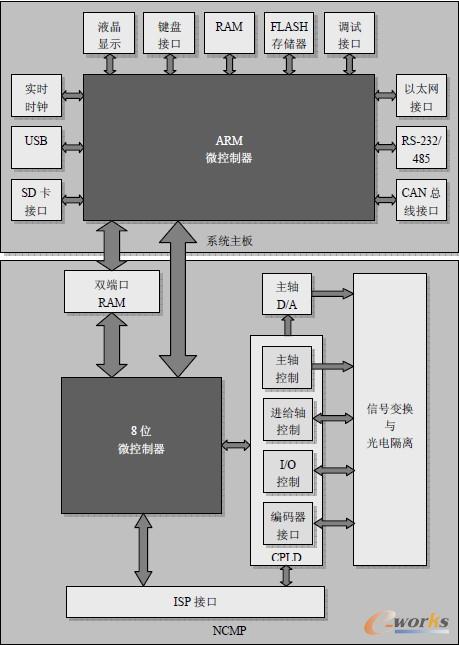

图8 是实验系统的硬件平台,图9 是实验平台的电路结构。为了验证数控流水线技术的跨平台开放特征,实验平台不是架构,而是基于当前在嵌入式领域广泛应用的 ARM 体系。NCMP 的主控制器选用入门级8 位单片机。NCM 执行器件主要采用低成本的CPLD 实现,实现了进给轴的DDA 算法控制,通用I/O 管理,主轴转速控制,数字编码器接口等功能。此外,为用户提供了主控制器和CPLD 的ISP 接口作为NCMP的重构接口。可见,与传统的基于PC 平台相比,实验平台具有成本极低、开放性好、硬件简单、可靠、无冗余,且不会被少数芯片厂商垄断等优点。软件平台采用了标准的 Linux 2.6 操作系统。Linux 操作系统具有源代码开放,内核可配置可剪裁,支持多种的不同体系的硬件平台,完善的网络协议和硬件驱动程序支持等优点,非常适合作为开放式数控系统的操作系统。实验中的数控流水线中各模块的基本功能:指令译码模块采用FANUC风格的G 代码指令体系,支持刀具补偿、固定循环、子程序、宏程序、坐标变换等高级功能;速度规划模块可实现梯形、S 曲线、三角函数等加减速算法,并具有速度前瞻功能;多轴插补模块支持2-4 轴的数据采样插补,支持直线、圆弧、螺旋线插补,并可实现直线轴与旋转轴的同步;专用I/模块可根据内置PLC 功能设定的用户控制逻辑进行I/O 控制,逻辑可由梯形图或指令表描述;杂项控制模块实现了延时处理、注释信息处理等机床动作规划的其他功能。本次实验中数控流水线线程中的各模块采用ANSI C 和ISO C++混合编写,在Windows XP 操作系统、Red Hat 9 Linux 操作系统(2.4 内核,PC 版本)及ARM-Linux 2.6 内核下进行了多平台的运行测试。结果表明,上述各模块源程序在不做任何修改的情况下可顺利地在不同软硬件平台下编译运行,具有良好的跨平台的开放特征。实验系统的管理线程中实现了加工状态数据和模态显示、自动运行、单段运行、多段运行、DNC 运行、程序编辑、内置/外部存储器管理、参数管理、加工轨迹三维仿真、系统交互诊断、网络通信等功能。NCMP 的主控制器的控制软件采用ANSI C 编写,并采用开放式的程序框架。NCMP 的CPLD逻辑通过Verilog HDL 语言描述,每个NCM 执行器件对应于Verilog 源程序中的一个模块。本次实验中模拟了对NCMP 的二次开发过程,对主控制器和NCM 执行器件的控制逻辑进行修改,并通过NCMP 的重构接口成功实施了对NCMP 的重构。这说明NCMP 的控制逻辑对使用者是完全开放的。

图8 实验系统硬件平台

图9 实验系统电路结构

- 上一篇文章:CNC加工中心的工艺特点

- 下一篇文章:三伺服机械手在注塑机的研究与应用