投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

基于CAM的10G EPON MAC/LLID多队列管理

0 引言

在EPON(Ethernet Passive Optical Network,以太无源光网络)系统中.OLT需要同时和多个ONU进行通信.准确无误地解析和发送数据是系统成功的关键之一。OLT根据LUD和MAC地址来寻找发送帧的目的地或查找接收帧的源地址.因此OLT系统内部必须拥有一个高速的LUD和MAC对应关系的查找表模块.这样才能完成相应的功能。

本文根据10G EPON全球化标准IEEE802.3av提出了一种利用CAM(Content Addressable Memory)IP核实现10G EPON OLT系统中MAC/LLID(Logical Link Identifier.逻辑链路标识)多队列管理的设计方案.并基于Xilinx公司的Vitex5 FXT FPGA开发平台进行设计开发和验证。

1 Xilinx CAM IP核

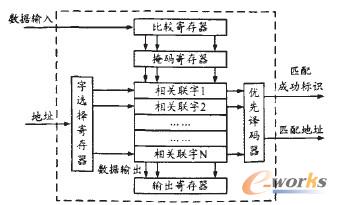

多数的存储器是基于地址串行查找.而CAM作为内容查找存储器在进行查找操作的时候不仅是并行的.而且采用阵列式存储方式,并提供优于其他搜索算法的操作性能.所以常被用在网络、通信、存储等等需要高速处理的场合。典型的CAM结构如图1所示。CAM的操作分为查找操作(也叫读操作、匹配操作)和写操作。

图1典型的CAM结构

当执行查找操作时.CAM接收到外部的输入匹配数据时,先将数据存储到比较寄存器中。掩码寄存器的功能是屏蔽无需比较的数据位。比较寄存器和掩码寄存器的内容共同组成一个查找字广播到存储器组中,与不同的相关联字进行并行匹配.结果被反馈到优先译码器中.得到一个具有最高优先权的匹配地址和匹配成功标识。

当执行写操作时.字选择寄存器会根据输入的地址来产生对l到N个相关联字进行操作的信号。

对FPGA器件来说.IP(Intellectual Propertyl就是已经设计好的模块.是待用的HDL代码或者网表级文件。Xilinx提供的CAM IP核具备典型CAM的功能。

2 10G EPON OLT MAC/LLID队列

EPON系统具有点到多点的拓扑结构.LLID在其中的作用是标识通过点到点仿真子层建立起来的逻辑链接.位于前导码的第六个字节到第七个字节。在一个EPON系统中.下行数据以广播方式传输到各个ONU,ONU接收自身LLID或者广播LLID的数据包。

根据IEEE 802.3av协议规定.在10G EPON OLT系统中.下行数据和上行数据在帧头替换时处理方式有所不同。数据在上行时需添加统一的以太标准帧头。而下行处理时需要根据每个帧的不同目的MAC地址添加对应的LLID.并要求对LLID域进行CRC8校验。因此.需要设计一个MAC/LLID查找添加模块。考虑到10G EPON系统具有高速的查找要求.所以在设计过程中采用CAM IP核来实现MAC/LLID存储部分。

3 利用CAM核实现MAC/LUD多队列管理

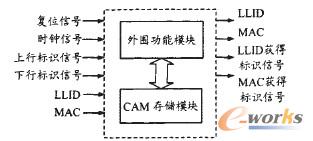

MAC/LLID多队列管理系统的总体框图如图2所示,主要分为2个模块,分别是CAM存储模块和外围功能模块。

图2 MAC/LLID多队列管理系统框图分页3.1 CAM存储模块

CAM存储模块主要实现多MAC的存储.利用CAM IP核实现。

假设每个ONU下带2个MAC.则16个ONU总计使用32个MAC地址。根据IEEE 802.3av中定义,若下行1Gb/s、上行IGb/s。LLID广播取值为Ox7FFF;若下行10Gb/s、上行1Gb/s(非对称10G系统)。亦或下行10Gb/s、上行10Gb/s(对称10G系统),LLID广播取值为0x7FFE:而0x7FFD~0x7F00为保留值。因此,根据协议规定.在逻辑设计中可取0x6F00~0x6FOF为16个LLID注册分配值。如此分配的LLID只有最后4比特不同.所以在逻辑设计中可将LLID映射为IP核的写入地址线.具体操作方法为:写入的地址线的后4位取自LLID的最后4个比特.地址线最高位区别一个LLID所带的2个不同的MAC。所以配置CAM深度为32,得到CAM输入信号wr_addr[4:0]。

根据以太帧格式.目的MAC地址为6个字节.所以配置CAM数据宽度为48比特.得到CAM输入信号din[47:0]。

3.2外围功能模块

CAM IP核的外围模块主要实现MAC或LLID在CAM中查询或者写入前的数据处理工作和之后的输出工作.这部分由逻辑设计完成。逻辑设计中特别定义了registered-nag[15:0]寄存器,寄存器中每一个比特位对应了16个LLID预定范围内的某个特定值。在注册的时候.与分配的LLID对应的REG相应位将置上,表示此LLID已被使用。利用此点可以很方便地在上行查找时验证LLID是否已经有效.或者利用这个REG删除CAM中存储的LLID/MAC数据。

外围模块实现的主要功能可以分为:注册(为多点控制协议MPCP中一部分.发生在上行)、上行查找、上行记录以及下行查找.

①注册:若ONU发送注册请求.OLT分配一个LLID给ONU.同时在LLID映射的地址线内将MAC值写入CAM。

②上行查找:OLT收到ONU发送的数据帧时.首先根据收到的LLID查找registered_flag[15:0]寄存器,判断该LLID是否有效。当LLID有效.则继续判断该帧的源MAC是否已经存入CAM中.方法是将该MAC值输入到CAM中进行匹配。若匹配.输出匹配MAC值。说明上行传输有效。

③上行记录:若上行MAC值在CAM中没有匹配项.则在LLID对应的地址线内将MAC值写入CAM中。与注册时写入不同的是.对应的地址线需变换最高位以区别2个不同的MAC。

④下行查找:当OLT收到一个下行数据的时候,判断该数据的目的MAC是否存储在CAM中。如果已存储,那么根据匹配所在的地址.根据映射规则.得到LLID.下行传输有效.以便于后续模块添加802.3av前导码;反之,不做操作。

3.3数据流实现

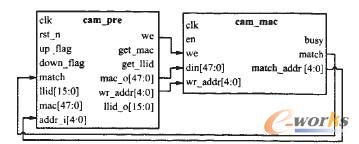

CAM存储模块和外围功能模块内部信号互连如图3所示,模块左列为输入项,右列为输出项。cam_pre模块实现CAM存储模块的外围功能,cam_mac是本设计中生成的CAM IP核。

图3 CAM模块和外围模块互连

当cam_pre模块接收到系统输入信号up_flag为高电平时,系统认为此时为上行数据流。锁存输入信号llid和mac。检查锁存的llid是否在预分配范围0x6F00~0x6FOF内。若不在此范围内,则认为ONU未注册,需要检查registered_flag[15:0]寄存器,寻找比特位为0的最低位位置.对应的Uid分配给未注册的ONU。同时registered_flag 寄存器对应位置为l,输出端we信号置为高电平.在 cam_mac中进行在LLID映射的地址线内存入锁存MAC值的操作。若锁存的llid在预分配范围.检查mac值是否在cam mac模块中记录:将we输出信号置为低电平.cam_pre 模块将锁存的mac信号输出到cam_mac中。在2个时钟周期内若有高电平match信号反馈到cam_pre中.则说明匹配成功.系统输出mac值和mac值获得标识信号;若无match反馈信号.说明此mac值未被记录到cam中.则输出端we信号置为高电平.在cam_mac中进行在LLID映射地址线内存人锁存MAC值的操作。

当cam_pre模块接收到系统输入信号down_flag为高电平时,系统认为此时为下行数据流。锁存输入信号llid和mac。检查mac值是否在cam_mac模块中记录:将we输出信号置为低电平,cam_pre模块将锁存的mac信号输出到cam_mac中。在2个时钟周期内若有高电平match信号反馈到cam_pre中.则说明匹配成功.cam_pre模块得到cam_mac模块反馈的地址,进行反映射操作得到llid值。系统输出Uid值和llid值获得标识信号:若无match反馈信号。则不做操作。一旦mac或llid获得标识信号输出高电平则说明上行或者下行传输数据帧可进行后续帧处理。

3.4仿真及结果讨论

在Xilinx virtex5平台上对设计进行编译综合。单独综合一个CAM核.最高速度205.255Mhz。系统期望速度200Mhz,若作为单系统仿真.由于输出信号和cam_mac的反馈信号有关.布线有延迟.所以系统综合速度只能达到150~160MHz。但本系统作为OLT系统的内部模块使用,所以输出端不设为output,则系统速度可达到200Mhz以上。调用Modelsim对设计进行仿真验证.得到的时序仿真结果如图4~图6所示。

图4 上行第一次注册仿真图

图5 上行记录MAC仿真图

图6 下行根据MAC查找LLID仿真图

从仿真结果可以看出.本设计能完成MAC/LLID多队列管理的基本功能,并具有单系统150MHz、内部模块200MHz的高处理速率。

4 结束语

本文基于IEEE 802.3av协议提出了一种利用Xilinx CAM IP核实现10G EPON OLT系统中MAC/LLID多队列管理的方法.并通过模块设计以及仿真验证.证明该方案能以200Mhz的内部模块处理速度应用在OLT系统中。

- 上一篇文章:涡轮机制造厂的Delcam应用

- 下一篇文章:半导体工艺线CAM及SPC的应用