投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

基于W5100的数控系统组网设计与实现

1.2 W5100 网络芯片简介

W5100 是目前比较流行的一款多功能的以太网网络接口芯片,内部集成了 10/100 兆以太网控制器,能够适用于高稳定、高集成、高性能和低成本的嵌入式系统。其内部集成了经过多年市场应用经验验证、且全硬件的 TCP/IP 协议栈、以太网介质传输层(MAC)以及物理层(PHY)。能够支持普遍的以太网协议,如TCP、UDP、IPv4、ICMP、ARP、IGMP 和 PPPoE,使得用户在使用 W5100 开发时不用过多了解以太网控制知识,主要具备简单的 Socket 编程基础就能够快速应用,从而解决了软件实现方式的稳定性和可靠性问题。简化的电路接口可以将 W5100 当做外部存储器一样访问,实现网络通信功能。W5100 具备的突出特点如下:

1) 支持自动通信握手(全双工和半双工);

2) 支持自动 MDI/MDIX,并自动校正信号极性;

3) 支持 ADSL 连接(支持 PPPoE 中的 PAP/CHAP 认证模式);

4) 支持 4 个独立端口同时运行;

5) 内部集成 16KB 数据收发缓存,默认每一个端口 4KB 缓冲大小。

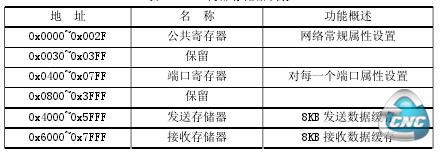

通过访问 W5100 内部寄存器实现控制,内部存储器映射如表 1 所示:

表 1 W5100 内部存储器映射

公共寄存器主要对网络配置、中断控制、超时处理参数以及缓冲区分配等进行设置,详细信息如表 2所示。其中,本文用到中断方式,W5100 提供 7 种中断源,任意一个未屏蔽中断触发时,中断输出引脚INT会保持低电平,CPU 通过 IR 寄存器确定中断源,得到处理后将 IR 相应位清零,完成中断处理状态。

表 2 W5100 公共寄存器功能描述

端口寄存器针对 4 个内部独立的通信端口进行设置,以 Sn_xx 的形式表示,主要描述了端口工作模式、端口号、端口目的物理地址和 IP 地址以及端口相关状态,具体功能可以参考有关用户应用手册。

1.3 硬件电路设计

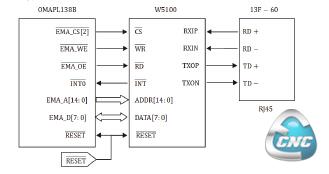

由于 W5100 可以当做外部存储器访问,OMAPL138B 提供了一个外部存储器接口(EMIFA,External MemoryInterface A),用于连接芯片到外部存储器,比如同步动态存储器(SDRAM)、低功耗 ROM 存储器和异步存储器,提供 8 位宽和 16 位宽访问能力。网络数控系统硬件电路设计主要涉及 EMIFA 与 W5100 连接,通过EMIFA 接口,使得 CPU 可以和 W5100 网络芯片很方便地进行数据传输。W5100 提供 3 种电路接口:间接并行总线、直接并行总线和 SPI 总线。间接并行总线只使用 ADDR[1:0]两个引脚,首先 CPU 将要读写的地址分别写入 IDM_AR0 和 IDM_AR1 寄存器,选中指定的寄存器,然后再从IDM_DR 寄存器中读写数据。因此访问单一寄存器时,间接并行总线方式需要 3 个总线周期,而直接并行总线方式访问只需要一个总线周期,本文采用直接并行总线方式连接设计。OMAPL138B 与 W5100 相关接口以及硬件电路总体框图如图 2 所示。

图 2 硬件电路总体框图

EMIFA 接口中处于 EMA_CS[5 :2]范围内的区间属于异步存储器控制器,本方案选择EMA_CS[2]作为W5100 片选,因此将 0x6000 0000~0x61FF FFFF(32MB)的地址空间分配给 W5100,基地址为 0x6000 0000。EMIFA 支持 8 位宽和 16 位宽访问,由于 W5100 寄存器为 8 位位宽,所以将 EMA_A[14:0]与 ADDR[14:0]相连。W5100 中断引脚低电平有效,与 OMAPL138 中断引脚 INT0连接。为了缩小电路接口设计的面积,采用10/100Mb/s 的 13F-60 自带网络变压器的 RJ45 以太网电路接口,W5100 的 RXIP 对应 RJ45 的 RD+,RXIN 对应 RD-,TXOP 对应 TD+,TXON 对应 TD-。

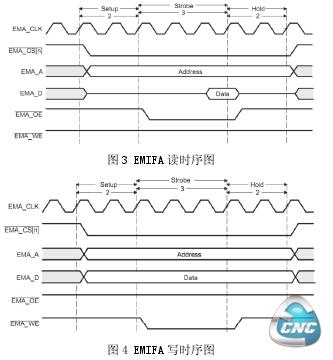

EMIFA 默认处于正常模式,访问时序有三个重要的阶段:Setup、Strobe 和 Hold period,这些时间的设置关系到与外部存储器进行读写操作的稳定性和正确性。EMIFA 读写时序图如图 3、4 所示,为了配合W5100 访问,分别将三个阶段设为 2、3、2 时间周期。在读操作的 Setup 阶段,地址总线引脚 EMA_A 开始有效并且EMA_CS[2]片选引脚为低电平,片选使能外部存储器设备;Strobe 阶段,EMA_OE读使能引脚为低电平,在该阶段最后一个周期 EMIFA 开始对数据总线引脚 EMA_D 进行采样并且EMA_OE变为高电平;Hold 阶段是数据的保持,EMIFA 将数据读取到内部寄存器,并且在该阶段最后一个周期地址总线引脚 EMA_A变为无效,EMA_CS[2]引脚变为高电平结束对外部存储器设备的片选使能。三个阶段时间周期通过 EMIFA寄存器 CEnCFG 的 R_SETUP、R_STROBE 和 R_HOLD 三个域进行设置,完成一次读操作。

在写操作的 Setup 阶段,地址总线引脚 EMA_A 和数据总线引脚 EMA_D 开始有效并且EMA_CS[2]片选引脚为低电平,片选使能外部存储器设备;Strobe 阶段,EMA_WE 写使能引脚为低电平,并将寄存器内数据写入外部存储器设备,在该阶段最后一个周期变为高电平;Hold 阶段最后一个周期地址总线引脚 EMA_A和数据总线引脚 EMA_D 变为无效,EMA_CS[2]引脚变为高电平结束对外部存储器设备的片选使能。三个阶段时间周期通过 EMIFA 寄存器 CEnCFG 的 W_SETUP、W_STROBE 和 W_HOLD 三个域进行设置,完成一次写操作。

- 第1页:基于W5100的数控系统组网设计与实现(1)

- 第2页:W5100 网络芯片简介

- 第3页:数控系统组网设计

- 第4页:PC 服务器软件设计

- 上一篇文章:基于多核ARM的数控系统的设计

- 下一篇文章:大型注塑机伺服驱动液压系统的优势分析