投稿邮箱:tb@e-works.net.cn

- 未来汽车工厂,在线下单支持私人定制

- 2018-02-02

- 基于云端的三维CAD系统Autodesk Fusion 360

- 2018-01-31

- 通过PTC物联网技术实现Flowserve泵的预测性维护

- 2018-01-31

- 微软预测性维护保障电梯高效服务

- 2018-01-30

数控系统软件模块实时调度方法(下)

2.5时间服务和数据约束

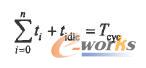

在数控系统中,当没有界面的运行指令信号时,通信触发信号定时触发调度申请,而通信触发信号的触发周期按照与运动控制的一次通信作为时钟周期,其时间基本上是固定并且是准确的,所以我们认为上位软件在插补周期内通信定时是可控的,并且满足

式中ti为第i个模块占用的时间,tidle为空闲时间,Teye,为系统插补周期。

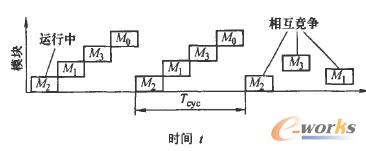

根据调度规则,各个模块占用CPU的时间是时变且不可控的,并且需要竞争获取,这就无法保证在一个插补周期内所有的模块都能够完整的运行,各模块在运行中模糊时间分配如图3所示。这就导致获取数据的充分性不能保证,为此我们在数据服务中采用缓冲的方式,并且在数据约束上采取更为稳健的策略。如在当前的数控系统中,采用了链表存储的数据结构,可以采用基于读者一写者问题的资源共享方式。在链式数据结构中,较为常用的是先进先出链表和环形链表,各实时模块负责写入数据链表或从链表中读取数据。作者采用了数据写入最大能力和读取数据的安全区域。也就是当写入数据时只有无法添加节点时才触发该模块的调度请求,而读数据过程中,如果所读取数据与写入数据的间距小于安全距离,则马上启动该模块的调度请求,申请调度写模块运行。

图3 实时模块模糊时间分配原理

2.6下位通信信号定时触发

由于在Windows系统中没有精确定时,通信触发信号为下位板卡通过串行通信的定时反馈,我们把与下位板卡通信的模块优先级设为最高等级,通过Windows提供的串行监测函数(Asynchronism())无限期等待,一旦下位信号返回,该函数马上被激活,该模块立即获得CPU资源。此时新一轮的调度再次开始。

3系统验证和数值仿真

3.1实时插补时间试验

在软件数控系统中,插补过程包括离线插补和实时插补。离线插补主要进行插补几何、速度、加减速的规划;而实时插补则完成时钟周期内的进给量的精确计算。在该系统中,我们对微细直线段进行了速度平滑处理,段与段之间采用直接速度过渡、速度微调过渡和直接减速过渡三种方式。其过渡方式的选择依据于前后直线在空间坐标系中所处的几何姿态。实时插补过程分为直线段插补准备和时钟周期插补。插补准备包括进给直线、圆弧的数据准备、加减速准备。根据加工命令的差异,插补准备分为以下几种准备类型:加工程序直线准备、加工程序圆弧准备、辅助加工准备(手动、下刀等)、急暂停插补准备和辅助二次动作插补准备。急暂停插补原理是根据命令镜像链表查找缓冲区延迟后的延迟脉冲和加工指令节点数据,根据延迟脉冲数据为起点进行插补准备和插补,得到的插补数据添加到延迟节点以后,其过程是直接减速的过程。

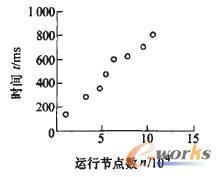

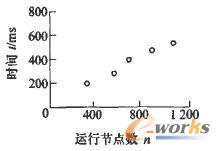

在软件数控系统上下位通信过程中,数据采用打包传输的方式,在没有数据资源约束和优先运行的情况下,插补模块连续运行,插补计算所得数据存放于脉冲缓冲区。为了验证占用实时处理的插补模块、通信模块和仿真模块的时间总和是否满足实时性需求。首先测试插补线程单独运行所需的时间。图4表示仅仅运行实时插补时,插补时间与运行节点数之间的关系,从图上可以看出即使是微小直线段插补,其平均一个插补周期计算所需的时间非常少,达到了0.01 ms左右。

图4 实时插补时间与运行节点数关系

3.2实时插补、仿真时间试验

实时插补仿真试验是同时进行插补计算和仿真,其中仿真的图形绘制独立于非实时模块的图形显示,在控制界面上显示加工轨迹和系统运行状态。因为界面模块的优先级最低,同时界面模块不参与线程调度,执行过程是在其他实时模块空闲时,根据接收的消息进行相应的执行动作。在实际的仿真中,为了保证界面模块能够在插补和仿真模块中间运行,仿真模块执行完毕后,使其在可设定的时间片内阻塞,然后再启动仿真模块申请其他模块的执行函数,而界面模块可以在其这个阻塞的时间片内执行相应的显示,仿真的速度也可以根据阻塞时间的长短调整。根据试验结果,如图5所示,平均每个插补周期中,仿真和插补两个模块占用的时间总和达到了0.5ms左右。

图5 实时插补和仿真时间与运行节点数关系

3.3应用实例与系统开发

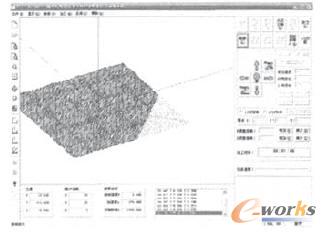

根据上述调度框架,我们在Windows 2000和XP系统下开发了基于PC的Soft型数控系统。软件系统开发采用VC++6.0平台,在该系统中我们选取插补时钟周期为2 ms,系统配置为CPU 2.0 GHz,256M DDR内存。在加工过程中没有出现通信时无数据可取的情况,软件系统所占的CPU百分比为40%左右。实际加工中采用8 ms的插补周期,图6为插补、仿真和通信实时运行的界面。

图6 插补、仿真和通信实时运行时界面

4结论

(1)采用基于优先级可变的模块模糊调度框架,能够解决Windows系统的非实时处理与数控系统的精确定时之间的矛盾。

(2)在资源约束和时间服务分配的基础上进行模块调度的优化配置,摒弃原有的模块精确定时方式,增加系统资源的自适应分配。

(3)采用该方法可以进一步推广应用于研究三层或三层以上的弱实时和强实时共存的软件数控系统,使得能够与CAD、CAM、CAPP系统的集成,如基于STEP-NC数控系统的开发。

- 上一篇文章:网络化设计和制造

- 下一篇文章:数控加工的可视化仿真